# Distributed Signal and Noise Modeling of Millimeter Wave Transistor Based on CMOS Technology

#### Z. Seifi, A. Abdipour, and R. Mirzavand

Electrical Engineering Department, Institute of Communications Technology and Applied Electromagnetics, Micro/mm-wave & Wireless Comm. Research Lab., Amirkabir University of Technology, Tehran, 15914, Iran z.seifi@aut.ac.ir, abdipour@aut.ac.ir, rmirzavand@aut.ac.ir

*Abstract* — This paper presents a complete distributed transmission line signal and noise modeling of millimeter wave CMOS transistor. In this model, the MOSFET transistor is considered as a three-coupled active transmission line structure, exciting by the noise equivalent sources distributed on its conductors. According to the transmission line theory, closed form expressions of the signal and noise parameters for a high frequency CMOS transistor are derived as the function of device width. By using the proposed model, the scattering and noise parameters of a 130 nm MOSFET are computed over a frequency range up to 100 GHz. The results obtained by this approach is compared with the lumped elements model and verified by the simulation results of Cadence SpectreRF simulator.

*Index Terms* — Cadence, CMOS transistor, coupled active transmission line, distributed transmission line model, lumped MOSFET model, millimeter wave.

#### **I. INTRODUCTION**

With the advancement in CMOS technology, the MOS transistors are scaled down into deep submicron regime with higher transit frequency. The high frequency capabilities of MOSFETs are very attractive for millimeter (mm) wave circuit design due to their ability of chip integration, low cost and low power consumption [1]. As the operating frequency of MOSFETs increases to the mm-wave range, the width of the device becomes comparable to the wave length. In such cases, the distributed transmission line effect needs to be considered accurately, in device modeling.

In previous works [2], [3] and [4] the distributed transmission line effect along the gate width has been studied. In these distributed models, the gate width is divided into finite number of slices that are connected together by using of series of scaled gate resistor. In [2], the thermal noise due to the gate resistance was incorporated in the model. In [3], MOSFET distributed model of [2] is improved by including the distributed charging resistance and the induced gate noise along the gate width. Nevertheless, in these studies only

distributed behavior of transistor along gate electrode width is modeled and other electrodes are ignored. Furthermore, the effects of the transmission line capacitances and inductances along the device width are not considered.

In this paper, a complete distributed transmission line signal and noise modeling of mm-wave MOSFET transistor that considered it as the excited three-coupled active transmission line structure, exciting by noise equivalent sources distributed on the conductors, is presented. The details of the proposed model are described in the next section. In Section III, the introduced approach is used in signal and noise modeling of 130 nm MOSFET and its results are discussed and compared with lumped and previous distributed models. Finally, the paper is concluded in the last section.

## II. DISTRIBUTED MM-WAVE MOSFET MODELING

#### A. Distributed signal analysis

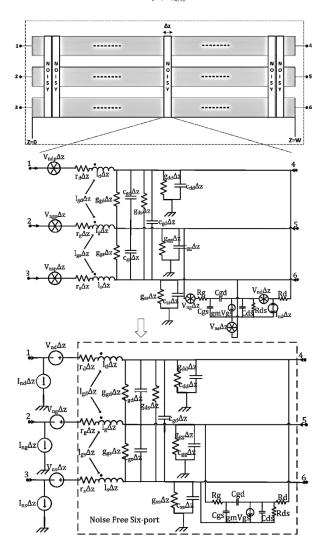

The proposed distributed model considers the MOSFET as three-coupled active transmission line, is shown in Fig. 1 (a). In this model, the device width is divided into an infinity number of segments, while each segment is separated into parallel intrinsic and extrinsic contributions. The parameters  $G_m$ ,  $C_{gs}$ ,  $C_{ds}$ ,  $C_{gd}$ ,  $R_g$ ,  $R_d$  and  $R_{ds}$  taken together are referred to as the intrinsic elements and standard BSIM4 model [5] is employed to compute them. BSIM4 is the physical MOSFET model supplied with Berkeley SPICE and models the channel current by using a complete single equation for both linear and saturation regions as:

$$I_{ds} = \frac{V_{dseff} I_{ds0} (V_{dseff})}{V_{dseff} + R_{ds} I_{ds0} (V_{dseff})} (1 + \frac{V_{ds} - V_{dseff}}{V_{A}})$$

$$(1 + \frac{V_{ds} - V_{dseff}}{V_{ASCBE}}),$$

(1)

and transistor conductance G<sub>m</sub> can be obtained as:

$$G_{\rm m} = \frac{\partial I_{\rm DS}}{\partial V_{\rm GS}} \bigg|_{V_{\rm DS} = {\rm Const.}}$$

(2)

Submitted On: May 11, 2014 Accepted On: May 25, 2015 The detailed equations of  $I_{ds0}$ ,  $V_{AscBE}$  and  $V_A$  have been given in [5]. In this model, capacitances are derived from the charges to ensure charge conservation. The space charge of a MOS structure consists of three fundamental components: the charge on the gate electrode,  $Q_G$ , the charge in the bulk depletion layer,  $Q_B$ , and the mobile charge in the channel region,  $Q_{INV}$ . Generally, the following relationship holds in a MOSFET:

$$Q_G + Q_{INV} + Q_B = 0, \qquad (3)$$

and

$$Q_{INV} = Q_D + Q_S, \qquad (4)$$

where  $Q_D$  and  $Q_S$  are the channel associated with the drain node and the source node, respectively. Capacitance between any two of the four terminals (gate, source, drain, and bulk) is defined as:

$$C_{ij} = \frac{\partial Q_i}{\partial V_j}, \quad i \text{ or } j \in (g, d, s, b).$$

(5)

BSIM4 provides three options for selecting different capacitance models. By selecting different capMod options, different model equations can be used to describe the characteristics of the charge and the capacitances [5]. In this model, the source/drain series resistances are modeled by a bias-independent diffusion resistance and bias-dependent LDD resistances. Accurate modeling of the bias-dependent LDD resistances is important for deep submicron CMOS technologies. The LDD source/drain resistance  $R_{ds}(V)$  is modeled internally through the I-V equation. The detailed relationships for modeling of intrinsic resistances have been given in [5]. Then the values of the per-unit-length intrinsic elements can be obtained by using scaling rules [6].

The extrinsic part models the transmission line and distributed behavior of transistor along the electrodes width. Therefore, the per-unit-length 3-by-3 square impedance and admittance matrices of transmission line MOSFET model, as a six-port structure, can be written as:

$$\begin{bmatrix} \hat{Y} \end{bmatrix} = \begin{bmatrix} \hat{Y}_{extrinsic} \end{bmatrix} + \begin{bmatrix} \hat{Y}_{intrinsic} \end{bmatrix}$$

$$= \begin{bmatrix} G \end{bmatrix} + j\omega \begin{bmatrix} C \end{bmatrix} + \begin{bmatrix} \hat{Y}_{ir} \end{bmatrix},$$

(6)

$$\left[\hat{Z}\right] = \left[Z_{s}\right] + j\omega\left[L\right] = \left[R\right] + j\omega\left[L_{i}\right] + j\omega\left[L\right], \tag{7}$$

where [C], [G] and [L] are the per-unit-length matrices of capacitance, conductance and inductance, respectively. The entries in these matrices can be obtained by applying numerical methods of calculating the per-unit-length parameters for multi-conductor transmission lines [7], according to the electrical and physical characteristics of the transistor. Furthermore,  $[Z_s]$  is the surface impedance matrix and demonstrates the distributed effects and frequency-dependent losses caused by the skin effect. The real part of  $[Z_s]$  represents the electrode resistance and the imaginary part, the internal inductance [6].  $[Y_{tr}]$  is used to model the intrinsic parallel part of the distributed transistor model. By applying the transmission line theory to the transistor model of Fig. 1 (b), the second-order coupled equations in the frequency-domain can be written as:

$$\frac{d^2[V]}{dz^2} = \frac{d^2}{dz^2} \Big[ \hat{V}_d \ \hat{V}_g \ \hat{V}_s \Big]^T = - \Big[ \hat{Z} \Big] \Big[ \hat{Y} \Big] \Big[ \hat{V} \Big], \tag{8}$$

$$\frac{d^{2}[\hat{I}]}{dz^{2}} = \frac{d^{2}}{dz^{2}} \Big[ \hat{I}_{d} \ \hat{I}_{g} \ \hat{I}_{s} \Big]^{T} = - \Big[ \hat{Y} \Big] \Big[ \hat{Z} \Big] \Big[ \hat{I} \Big], \tag{9}$$

where [V] and [I] are 1-by-3 voltage and current matrices of electrodes, respectively and functions of z and  $\omega$ . For solving the above equations, the well-known similarity transformation solution is used [8]. By implementing this method, the general solutions for the voltages and current matrices can be obtained as:

$$\begin{bmatrix} \hat{V} \end{bmatrix} = \begin{bmatrix} \hat{T}_{V} \end{bmatrix} \left( \begin{bmatrix} e^{-\hat{\gamma}z} \end{bmatrix} \begin{bmatrix} \hat{V}_{m}^{+} \end{bmatrix} + \begin{bmatrix} e^{+\hat{\gamma}z} \end{bmatrix} \begin{bmatrix} \hat{V}_{m}^{-} \end{bmatrix} \right), \quad (10)$$

$$\begin{bmatrix} \hat{I} \end{bmatrix} = \begin{bmatrix} \hat{Y}_c \end{bmatrix} \begin{bmatrix} \hat{T}_v \end{bmatrix} \left( \begin{bmatrix} e^{-\hat{\gamma}z} \end{bmatrix} \begin{bmatrix} \hat{V}_m^+ \end{bmatrix} - \begin{bmatrix} e^{+\hat{\gamma}z} \end{bmatrix} \begin{bmatrix} \hat{V}_m^- \end{bmatrix} \right), \quad (11)$$

where  $[\hat{Y}_c] = [\hat{Z}]^{-1} [\hat{T}_v] [\hat{\gamma}] [\hat{T}_v]^{-1}$  is defined as characteristic admittance matrix. The elements of  $[\hat{\gamma}]$  and  $[\hat{T}_v]$ matrices are the eigenvalues and eigenvectors of  $[\hat{Z}] [\hat{Y}_c]$ , respectively. By evaluating the general forms of the solutions in (10) and (11) at z = 0 and z = W and omitting the unknown coefficients  $[\hat{V}_m^{\pm}]$ , the 6-by-6 chain matrix of MOSFET model shown in Fig. 1 (b), which can be transformed to the scattering matrix form, will be obtained as follows:

$$\begin{split} \left[\hat{V},\hat{I}\right]_{(W,\omega)}^{T} &= -\hat{\Phi}\Big|_{(W)} \left[\hat{V},\hat{I}\right]_{(0,\omega)}^{T} \\ &= \begin{bmatrix} \hat{\Phi}_{11\ 3\times3} & \hat{\Phi}_{12\ 3\times3} \\ \hat{\Phi}_{21\ 3\times3} & \hat{\Phi}_{22\ 3\times3} \end{bmatrix}_{(W)} \left[\hat{V},\hat{I}\right]_{(0,\omega)}^{T}, \end{split} \tag{12} \\ &\hat{\Phi}_{11}\Big|_{(W)} = \frac{1}{2}\hat{T}_{V}\left(e^{\hat{\gamma}W} + e^{-\hat{\gamma}W}\right)\hat{T}_{V}^{-1}, \\ &\hat{\Phi}_{12}\Big|_{(W)} = -\frac{1}{2}\hat{T}_{V}\left(e^{\hat{\gamma}W} - e^{-\hat{\gamma}W}\right)\hat{\gamma}^{-1}\hat{T}_{V}^{-1}\hat{Z}, \\ &\hat{\Phi}_{21}\Big|_{(W)} = -\frac{1}{2}\hat{Y}_{c}\left[\hat{T}_{V}\left(e^{\hat{\gamma}W} - e^{-\hat{\gamma}W}\right)\hat{T}_{V}^{-1}\right], \\ &\hat{\Phi}_{22}\Big|_{(W)} = \frac{1}{2}\hat{Z}^{-1}\hat{T}_{V}\left(e^{\hat{\gamma}W} + e^{-\hat{\gamma}W}\right)\hat{T}_{V}^{-1}\hat{Z}. \end{split}$$

Fig. 1. (a) Differential part of distributed signal model of the mm-wave MOSFET, and (b) the six-port distributed transmission line model of MOSFET.

# B. Distributed noise analysis of millimeter wave MOSFET

To consider the distributed electrodes width effect, the excited three-coupled transmission line structure, exciting by noise equivalent sources distributed on the conductors, is proposed for modeling of noise performance of millimeter wave MOSSFETs. A full description of the proposed model is clearly shown in Fig. 2. The noise originated within the active region is computed by using BSIM4 model [5]. It includes the flicker noise, channel thermal noise, induced gate noise and their correlation and thermal noise due to the resistances at the terminals. Two flicker noise models are included in BSIM4. In this paper, unified physical flicker noise model is used. In this model, the spectral drain current noise power density is formulated as:

$$S_{id}(f) = \frac{S_{id,inv}(f) \cdot S_{id,sub}(f)}{S_{id,inv}(f) + S_{id,sub}(f)},$$

(14)

where  $S_{id,inv}(f)$  and  $S_{id,sub}(f)$  are the spectral drain current noise power density of the device in the inversion and the sub-threshold regions, respectively, which the detailed equations of them have been given in [5]. Such as flicker noise, two options for the channel thermal noise are provided in BSIM4. One is the charge-based model from BSIM3v3 and the other is the holistic model. In the holistic model, which is used in this paper, all the short-channel effects including the velocity saturation effect incorporated in the I–V model as well as the induced gate noise with partial correlation to the channel thermal noise are all captured in the new "noise partition" model. In this model, two current and voltage noise source is used for modeling. The noise voltage source partitioned to the source side is given by:

$$\overline{v_d^2} = 4k_B T \theta_{inoi} \frac{V_{\text{dseff}} \Delta f}{I_{\text{DS}}},$$

(15)

and the noise current source put in the channel region with gate and body amplication is given by:

$$\overline{i_d^2} = \frac{4k_B \mathrm{TV}_{\mathrm{dseff}} \Delta f}{\mathrm{I}_{\mathrm{DS}}} \left[ G_{\mathrm{DS}} + \beta_{\mathrm{tnoi}} (G_m + G_{\mathrm{mbs}}) \right]^2$$

$$- \overline{v_d^2} \left( G_{\mathrm{DS}} + G_m + G_{\mathrm{mbs}} \right)^2.$$

(16)

Finally, the power spectral density of the thermal noise current from the electrodes resistance is given by [5]:

$$S_{it,R_{g,d,s}} = \frac{4K_B T}{R_{g,d,s}} \cdot \frac{1}{2}.$$

(17)

Aside from the intrinsic noise sources, the thermal noise generated within the passive part is considered. By considering the noise sources as excited sources, the transistor noise behavior can be analyzed by using excited multi conductor transmission lines solutions [9].

As shown in Fig. 2, all the noise sources of any differential subsections of the model can be transformed into correlated input-referred voltage and current noise sources of a noise free network, by using circuit analysis [10]. Then, by using Kirchhoff's voltage (KVL) and current (KCL) laws for the differential segment, the frequency domain coupled first-order ordinary differential equations of the noise transmission line model of the transistor will be obtained:

$$\frac{d}{dz}\begin{bmatrix} \hat{V}\\ \hat{I} \end{bmatrix}_{(z,\omega)} = \begin{bmatrix} 0 & -\hat{Z}\\ -\hat{Y} & 0 \end{bmatrix} \begin{bmatrix} \hat{V}\\ \hat{I} \end{bmatrix}_{(z,\omega)} + \begin{bmatrix} \hat{v}_n\\ \hat{i}_n \end{bmatrix}_{(z)}, \quad (18)$$

where  $[\hat{v}_n]_{(z)}$  and  $[\hat{i}_n]_{(z)}$  are 1-by-3 matrices of the linear density of voltage and current noise sources, respectively. Equation (18) is in the same form as state-variable equation, thus the solution of it can be written as [11]:

$$\begin{bmatrix} \hat{V} \\ \hat{I} \end{bmatrix}_{(z,\omega)} = \hat{\Phi} \Big|_{(z-z_0)} \begin{bmatrix} \hat{V} \\ \hat{I} \end{bmatrix}_{(z_0,\omega)} + \int_{z_0}^{z} \hat{\Phi} \Big|_{(z-\tau)} \begin{bmatrix} \hat{v}_n \\ \hat{i}_n \end{bmatrix}_{(z)} d\tau.$$

(19)

By substituting  $z_0 = 0$  and z = W, the effect of the internal noise sources on the voltage and current of the transistor port can be determined as follows:

$$\begin{bmatrix} \hat{V} \\ \hat{I} \end{bmatrix}_{(W,\omega)} = \begin{bmatrix} \hat{\Phi}_{11} & \hat{\Phi}_{12} \\ \hat{\Phi}_{21} & \hat{\Phi}_{22} \end{bmatrix}_{(W)} \begin{bmatrix} \hat{V} \\ \hat{I} \end{bmatrix}_{(0,\omega)} + \begin{bmatrix} \hat{V}_{NT} \\ \hat{I}_{NT} \end{bmatrix}_{(W)}, \quad (20)$$

where:

$$\begin{bmatrix} \hat{V}_{NT} \\ \hat{I}_{NT} \end{bmatrix}_{(W)} = \underbrace{\bigcup_{0}^{W} \begin{bmatrix} \hat{\Phi}_{11} & \hat{\Phi}_{12} \\ \hat{\Phi}_{21} & \hat{\Phi}_{22} \end{bmatrix}_{(\tau)}}_{(\hat{A}(W))_{k\neq 0}} d\tau \cdot \begin{bmatrix} \hat{v}_{n} \\ \hat{i}_{n} \end{bmatrix}.$$

(21)

Fig. 2. Complete details of distributed noise model of the mm-wave MOSFET as excited three-coupled transmission line structure.

The distributed noise sources of differential part in (21) are assumed to be independent of the device width, since the BSIM4 model is chosen for them. The correlation matrix for admittance representation can be obtained by determination of the currents in short-circuited ports of transistor [12]. By enforcing boundary conditions to equation (20), the noise currents at the

short-circuited ports, as a six-port active network, can be written in the following matrix form:

$$\begin{bmatrix} \hat{I}_{n0} \\ \hat{I}_{nW} \end{bmatrix} = \begin{bmatrix} -\hat{I} \\ |_{(0,\omega)} \\ +\hat{I} \\ |_{(W,\omega)} \end{bmatrix} = \begin{bmatrix} \hat{Z}^{-1} & \mathbf{K} \\ -\hat{Z}^{-1} & \mathbf{K} \end{bmatrix} \times \begin{bmatrix} \hat{v}_n \\ \hat{i}_n \end{bmatrix}, \quad (22)$$

for  $K = -\hat{T}_I \hat{\gamma}^{-1} \sinh^{-1}(\hat{\gamma}W)(\cosh(\hat{\gamma}W) - \mathbf{1}_{3\times 3})\hat{T}_I^{-1}$ . Finally, the correlation matrix for admittance representation of the six-port noise model of the MOSFET can be written as equation (23). CAU is the per-unit-length noise correlation matrix for chain representation of the transistor:

$$CY_{tr} = \begin{bmatrix} I_{n0} \\ I_{nW} \end{bmatrix} \begin{bmatrix} I_{n0} \\ I_{nW} \end{bmatrix}^{\dagger} = P \underbrace{\begin{bmatrix} \hat{v}_n \\ \hat{i}_n \end{bmatrix} \begin{bmatrix} \hat{v}_n \\ \hat{i}_n \end{bmatrix}}_{CAU} P^{\dagger}.$$

(23)

#### **III. RESULTS AND DISCUSSION**

The proposed approach is used for modeling of a 130 nm bulk CMOS transistor. It is sufficient to consider introduced model for a single finger structure. Multiple fingers transistors can be accounted as parallel multiple single finger transistors. The transistor is biased at Vds = 1.2 V and Ids = 7 mA. As was mentioned in the previous section, the BSIM4 model [5], is used to compute elements and noise sources of active part and the per-unit-length parameters of passive part is evaluated by using numerical method of moments technique [7]. As shown in Fig. 1, the beginning of the gate and the end of drain electrodes are considered as the input and output nodes, respectively. Moreover, the source electrodes are grounded.

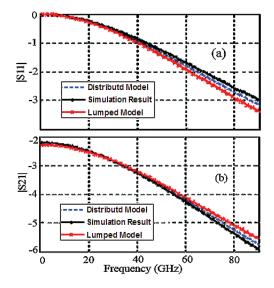

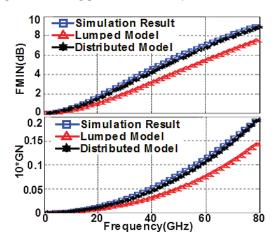

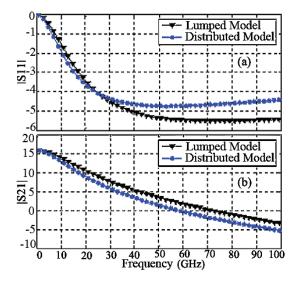

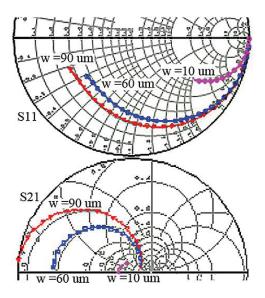

The scattering and noise parameters of proposed distributed model and Cadence SpectreRF post-layout simulation results are displayed in Figs. 3 and 4, for an NMOS transistor with gate width of 10 µm. The excellent broadband accuracy of the distributed model compared to the simulation results verifies that the introduced model is correct and complete. Furthermore, comparing these curves with lumped model, one can see that third models agreed well at low frequency but at high frequencies, the distributed effects of the transmission line capacitances and inductances along the device width become significant and can no longer be ignored. The scattering parameters of the transistor with gate width of 90 µm, over a frequency range of DC-100 GHz, calculated by using proposed distributed and lumped models are drawn in Fig. 5. The results clearly show that the distributed and lumped models are the same at the low frequency and by increasing the frequency, the difference between two models also increasing. The S11 and S21 of the transistor for three values of the gate width, 10, 60 and 90 µm, are plotted in Fig. 6.

Fig. 3. Scattering parameters of 10 µm MOSFET.

Fig. 4. Noise parameters of 10 µm MOSFET.

Fig. 5. Scattering parameters of 90 µm MOSFET.

Fig. 6. Scattering parameters of 10, 60, and 90  $\mu$ m MOSFETs computed by distributed model.

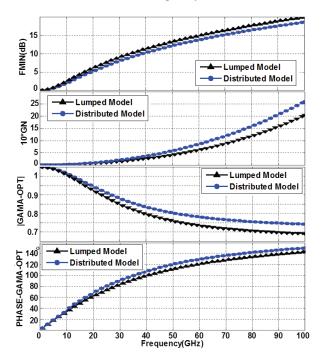

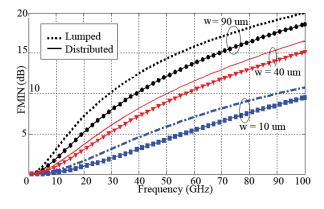

By using introduced model, four noise parameters, including minimum noise figure, normalized equivalent noise admittance, the amplitude and the phase of optimum reflection coefficient, are plotted in Fig. 7 and compared with lumped model. Moreover, Fig. 8 shows the behavior of minimum noise figure of the transistor for the different values of the gate width. Studying these figures illustrates the importance of distributed transmission line modeling of MOSFET by increasing the device width and the frequency.

Fig. 7. Noise parameters of the MOSFET.

Fig. 8. Minimum noise figure of the MOSFET.

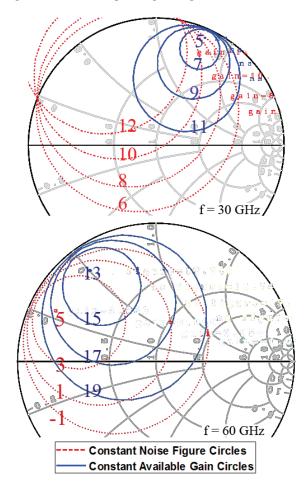

Figure 9 demonstrates the constant noise figure and available power gain circles of the MOSFET at 20 and 60 GHz. Thus, based on the information obtained from the proposed approach, accurate design of mm-wave circuits, containing the MOSFET, for a specified noise figure and available power gain is possible.

Fig. 9. Constant noise figure and available gain circles calculated by distributed model for f = 30 and 60 GHz.

#### **IV. CONCLUSION**

As the operating frequency of MOSFETs increases to the mm-wave range, the width of the device become comparable to the wave length. In such cases, the distributed transmission line effect needs to be considered accurately, in device modeling. According to that in the previous lumped models this effect wasn't considered, this paper introduces a new distributed transmission line signal and noise modeling and analysis of mm-wave MOSFET transistor. In this model, the MOSFET transistor is considered as the excited threecoupled active transmission line structure, exciting by noise equivalent sources distributed on its conductors. Comparing the signal and noise parameters of MOSFET calculated with the proposed distributed model and lumped model was shown that two models have the same results at low frequencies. But, by increasing frequency to the mm-wave range, where the electrodes widths are comparable with the wavelength, a difference appears between the results of two models. It is demonstrated that the distributed effects of the transmission line along the device width become significant and can no longer be ignored. Therefore, the accuracy of high-frequency noise simulation in the Nano-scale RF CMOS transistors can be facilitated by using the proposed model. Moreover, based on the proposed modeling approach, the influence of important factors such as the effect of electrode loading and the location and number of excitation/ extraction contact points, can be investigated and optimized for improving the performance of the mmwave MOSFETs.

### REFERENCES

- A. M. Niknejad and H. Hashemi, *mm-Wave Silicon Technology* 60 GHz and Beyond, Springer Science+Business Media, LLC, 2008.

- [2] B. Razavi, R.-H. Yan, and K. F. Lee, "Impact of distributed gate resistance on the performance of MOS devices," *IEEE Trans. Circuits Syst. I*, vol. 41, pp. 750-754, Nov. 1994.

- [3] E. Abou-Allam and T. Manku, "An improved transmission-line model for MOS transistors, *IEEE Transactions on Circuits and Systems - II: Analog and Digital Signal Processing*, vol. 46, no. 11, Nov. 1999.

- [4] Y. Lin, M. Obrecht, and T. Manku, "RF noise characterization of MOS devices for LNA design using a physical-based quasi-3-D approach," *IEEE Transactions on Circuits and Systems - II: Analog and Digital Signal Processing*, vol. 48, no. 10, Oct. 2001.

- [5] The BSIM 4.4 Manual, http://www-device.eecs. berkeley.edu/bsim4.

- [6] A. Abdipour and A. Pacauds, "Complete sliced model of microwave FETs & comparison with

lumped model & experimental results," *IEEE Trans. on MTT*, vol. MTT-44, pp. 4-9, Jan. 1996.

- [7] C. R. Paul, Analysis of Multiconductor Transmission Lines, 2<sup>nd</sup> edition, John Wiley & Sons, Inc., Hoboken, New Jersey, 2008.

- [8] F. E. Hohn, *Elementary Matrix Algebra*, 2<sup>nd</sup> edition, Macmillan, New York, 1964.

- [9] F. M. Tesche, T. K. Liu, S. K. Chang, and D. V. Giri, "Field excitation of multiconductor transmission lines," *Technical Report AFWL-TR-78-185*, Air Force Weapons Lab, Albuquerque, NM, 1979.

- [10] B. Razavi, *RF Microelectronics. Upper Saddle River*, NJ: Prentice-Hall, 1998.

- [11] "Useful matrix chain parameter identities for the analysis of multiconductor transmission lines," *IEEE Transactions on Microwave Theory and Techniques*, 23(9), 756-760, 1975.

- [12] H. A. Haus and R. B. Adler, Circuit Theory of Linear Noisy Networks, M.I.T. Press, 1959.

Zahra Seifi was born in Iran in 1988. She obtained his B.Sc. in Electrical Engineering in 2011 and the M.Sc. in Communication in 2013 from Amirkabir University, Tehran, Iran. Her research areas include High frequency signal and noise EM modeling of active

devices and circuits and RF, microwave and mm-wave MMIC circuit design .She is currently a Ph.D. student at Amirkabir University of Technology.

Abdolali Abdipour was born in Alashtar, Iran, in 1966. He received his B.Sc. degree in Electrical Engineering from Tehran University, Tehran, Iran, in 1989, his M.Sc. degree in Electronics from Limoges University, Limoges, France, in 1992, and his Ph.D. degree in

Electronic Engineering from Paris XI University, Paris,

France, in 1996. He is currently a Professor with the Electrical Engineering Department, Amirkabir University of Technology (Tehran Polytechnic), Tehran, Iran. He has authored four books in Persian and authored or co-authored over 300 papers in refereed journals and local and international conferences. His research areas include wireless communication systems, RF/microwave/millimeter-wave circuit and system design, electromagnetic modeling of active devices and circuits, high-frequency electronics (signal and noise), and nonlinear modeling. Currently, he is Director of the Institute of Communications Tech. and Applied Electromagnetics, Amirkabir University of Technology, Tehran, Iran.

**Rashid Mirzavand** received the B.Sc. degree from Isfahan University of Technology, Isfahan, Iran, in 2004, M.Sc. and Ph.D. degrees from Amirkabir University of Technology, Tehran, Iran, in 2007 and 2011, all in Electrical Engineering. In 2009, he joined the Centre for Analysis,

Scientific Computing and Applications, Eindhoven University of Technology, Eindhoven, The Netherlands, as a visiting Ph.D. student. Since 2011, he is a Research Assistant Professor with the Institute of Communications Tech. and Applied Electromagnetics, Amirkabir University of Technology, Tehran, Iran. He is the recipient of the Alberta Innovates Technology Futures (AITF) Post-doctoral Fellowship and is currently a Research Associate with the Intelligent Wireless Technology Laboratory, University of Alberta, Edmonton, Canada. His research interests are in the areas of intelligent integrated sensors and antennas, Microwave & mm-wave circuits and wireless systems, and computational electromagnetic.